推挽输出与开漏输出 软件开发中的硬件接口理解与应用

在嵌入式软件开发中,深入理解硬件接口的工作模式是编写稳定、高效代码的基础。推挽输出(Push-Pull Output)和开漏输出(Open-Drain Output)是两种常见的数字输出电路结构,它们在软件配置、驱动能力和应用场景上有着显著差异。掌握这些差异,对于软件工程师进行外设驱动开发、通信协议实现及系统功耗优化至关重要。

一、核心概念与硬件原理

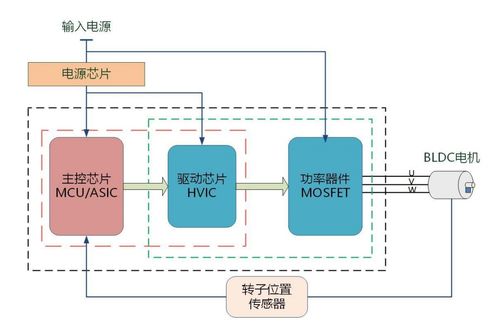

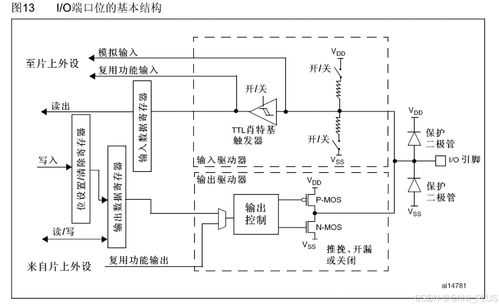

推挽输出采用两个晶体管(通常为MOSFET)组成推挽结构。其中一个负责将输出拉高至电源电压(如VCC),另一个负责将输出拉低至地(GND)。在任意时刻,只有一个晶体管导通,使得输出电平要么为高(逻辑1),要么为低(逻辑0),具有明确的驱动能力和低输出阻抗。其优点在于能够直接驱动较大电流负载(如LED、小型继电器),且信号边沿陡峭,适合高速数字信号传输。

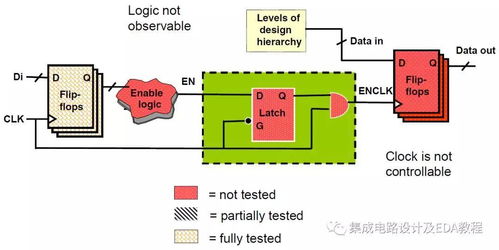

开漏输出(在CMOS工艺中常称为开集输出,Open-Collector)仅使用一个下拉晶体管连接到地,而没有内部上拉至电源。当晶体管关闭时,输出处于高阻态(悬空);当晶体管导通时,输出被拉低至地(逻辑0)。因此,开漏输出本身无法主动输出高电平,必须依赖外部上拉电阻连接到电源,才能实现完整的高低电平输出。这种结构支持“线与”(Wired-AND)功能,即多个开漏输出可以直接连接在一起,通过外部上拉电阻共享,任一输出拉低则总线为低。

二、软件开发中的配置与操作

在软件层面,这两种输出模式通常通过微控制器的GPIO(通用输入输出)寄存器进行配置。以常见的ARM Cortex-M系列微控制器为例:

- 推挽输出配置:在初始化阶段,软件需设置GPIO模式寄存器为输出模式,并选择推挽类型。例如,在STM32的HAL库中,可通过

GPIO<em>InitStruct.Mode = GPIO</em>MODE<em>OUTPUT</em>PP进行设置。输出电平时,直接写入输出数据寄存器(如HAL<em>GPIO</em>WritePin())即可控制高低电平,无需外部电路干预。

- 开漏输出配置:配置为开漏模式(如

GPIO<em>MODE</em>OUTPUT_OD)。此时,软件在输出高电平时,实际上只是关闭了下拉晶体管,输出依靠外部上拉电阻拉到高电平。因此,在驱动开漏输出时,需要确保外部上拉电阻已正确连接,否则读取引脚电平可能不确定。开漏输出特别适用于双向通信总线(如I2C),因为同一引脚可以兼作输入和输出,通过“线与”机制实现多主设备仲裁。

三、典型应用场景与软件策略

- 推挽输出的应用:

- 直接驱动负载:如控制LED亮灭、蜂鸣器发声,软件只需简单写入高低电平。

- 高速数字接口:如SPI、USART的TX引脚,要求快速电平切换,推挽输出能提供清晰的信号边沿。

- 电源开关控制:通过驱动MOSFET栅极,控制大功率电路通断。

- 开漏输出的应用:

- I2C通信协议:I2C的SDA和SCL线必须使用开漏输出,以支持多设备共享总线。软件在实现I2C驱动时,需注意释放总线(输出高电平)实则是将引脚配置为高阻,依赖上拉电阻拉高。

- 电平转换:当不同电压域的器件需要通信时(如3.3V MCU与5V传感器),开漏输出配合外部上拉至目标电压,可以安全实现电平匹配,避免损坏低压器件。

- 中断共享与唤醒信号:多个开漏输出连接至一个中断引脚,任一设备拉低即可触发中断,软件再通过轮询识别中断源。

四、软件设计注意事项

- 上拉电阻配置:使用开漏输出时,软件工程师需与硬件工程师确认上拉电阻的值(通常1kΩ~10kΩ),电阻过大会导致上升沿缓慢,影响通信速率;过小则增加功耗。在软件模拟时序(如I2C、One-Wire)时,需根据实际上升时间调整延时。

- 初始状态管理:系统上电时,GPIO状态可能不确定。软件应在初始化阶段明确设置输出模式及初始电平,特别是开漏输出,若意外输出低电平可能导致总线冲突。

- 功耗优化:推挽输出在静态时可能产生穿透电流(如果同时导通,但现代MCU通常避免),而开漏输出在高电平状态依赖上拉电阻,会有持续电流消耗。在低功耗设计中,需合理选择模式,并在空闲时将引脚切换为高阻输入或推挽输出固定电平。

- 故障诊断:在调试通信故障时,软件可配合逻辑分析仪,检查开漏总线的上升时间是否过慢(由上拉电阻和寄生电容导致),这可能需要软件降低通信速率或调整硬件参数。

五、

推挽输出和开漏输出是嵌入式软件与硬件交互的桥梁。软件开发者不能仅停留在配置寄存器层面,而应理解其电路特性,从而做出合理的设计选择:推挽输出适用于需要强驱动、高速单端信号的场景;开漏输出则为共享总线、电平转换和双向通信提供了灵活解决方案。在实际项目中,结合具体硬件手册和协议要求,正确配置并优化这些接口,是提升系统可靠性、性能及能效的关键一步。通过软硬协同的思维,开发者能够更高效地解决复杂的嵌入式系统挑战。

如若转载,请注明出处:http://www.xiangchebaitiao.com/product/49.html

更新时间:2026-02-24 19:31:33