数字集成电路设计(二) Verilog HDL基础知识与集成电路设计服务

数字集成电路设计是现代电子工程领域的核心技术之一,而Verilog HDL作为主流的硬件描述语言,在其中扮演着至关重要的角色。本文将从Verilog HDL的基础知识入手,并探讨集成电路设计服务的相关内容。

一、Verilog HDL基础知识

Verilog HDL(硬件描述语言)是一种用于数字系统建模、设计和验证的语言。它支持从系统级到门级的多层次抽象描述,能够高效地描述数字电路的结构和行为。

1. 基本语法结构

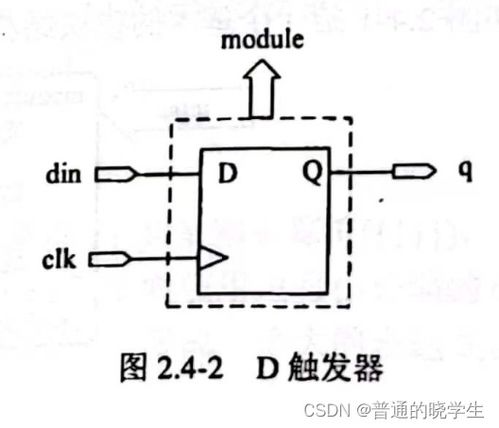

Verilog HDL包含模块(module)、端口(port)、信号(wire/reg)等基本元素。模块是Verilog设计的基本单元,通过端口与外部环境交互。信号分为线网类型(wire)和寄存器类型(reg),分别用于连接组合逻辑和存储时序逻辑。

2. 数据类型与运算符

Verilog支持多种数据类型,包括标量(scalar)、向量(vector)和数组(array)。常用的运算符包括算术运算符、关系运算符、逻辑运算符和位运算符等,这些运算符的组合能够描述复杂的数字逻辑功能。

3. 行为级建模

通过always块和initial块,Verilog可以描述电路的行为。always块用于描述重复执行的逻辑,而initial块仅在仿真开始时执行一次。这些结构使得设计者能够以类似软件编程的方式描述硬件行为。

4. 结构级建模

Verilog支持通过实例化已有模块来构建更大的系统,这种层次化设计方法大大提高了代码的可重用性和可维护性。

二、集成电路设计服务

随着半导体技术的不断发展,专业的集成电路设计服务变得越来越重要。这些服务涵盖了从概念到成品的全过程,主要包括:

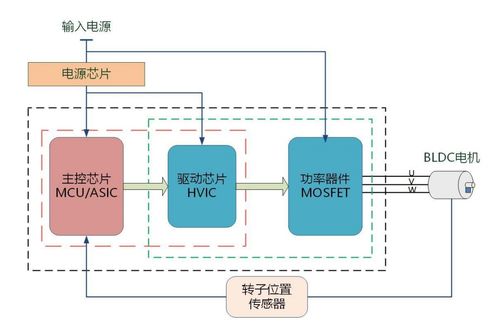

1. 架构设计

根据客户需求,设计团队会确定芯片的整体架构,包括功能模块划分、接口定义和性能指标等。

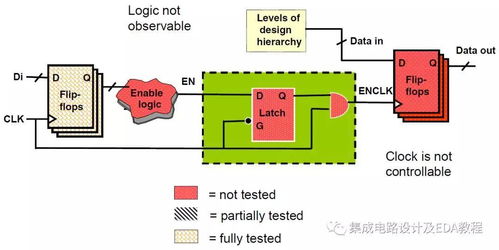

2. RTL设计与验证

使用Verilog等硬件描述语言进行寄存器传输级(RTL)设计,并通过仿真验证其功能正确性。这一阶段通常需要编写大量的测试用例,确保设计满足规格要求。

3. 逻辑综合与时序分析

将RTL代码转换为门级网表,并进行时序分析以确保电路能够在目标频率下稳定工作。

4. 物理设计

包括布局规划、布线、时钟树综合等步骤,将逻辑设计转换为实际的物理版图。

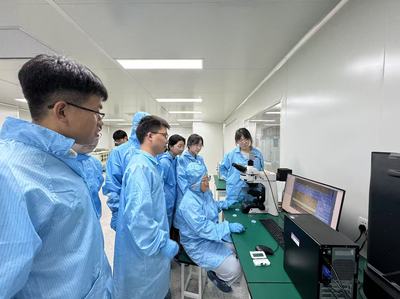

5. 测试与封装

设计完成后,需要进行芯片测试和封装,确保最终产品符合质量和可靠性要求。

专业的集成电路设计服务提供商通常拥有丰富的项目经验和先进的设计工具,能够为客户提供从概念到量产的全流程解决方案。随着AI、物联网等新兴技术的发展,对高性能、低功耗数字集成电路的需求日益增长,Verilog HDL和专业的IC设计服务将继续在推动技术进步方面发挥关键作用。

如若转载,请注明出处:http://www.xiangchebaitiao.com/product/38.html

更新时间:2026-02-24 21:37:00